-

CNN Accelerator

A convolutional neural network (CNN) is a network architecture for deep learning that learns directly from data. CNNs are particularly effective at finding patterns in images to recognize objects, classes, and categories. This function is also expected to be used in various parts of future calculation processing to improve processing. In that sense, it becomes important as a core IP. We have obtained new design results for the CNN accelerator Resnet50.

ve obtained new design results for the CNN accelerator Resnet50.

-

Block LU Factorization

Block LU decomposition provides a parallel algorithm that efficiently performs LU decomposition of a matrix in parallel. By applying the task scheduling method already obtained in our project to this block LU decomposition, we demonstrate the derivation of parallel scheduling with higher performance than conventional methods.

-

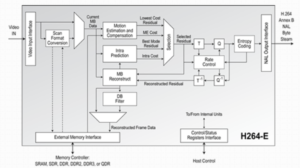

H.264 Video Codec

Video codec H.264 is a standardized technology for compressing and decoding video input of 1920 x 1080 pixels at 60 frames per second. Advanced data parallelization is performed on data for each 16x16 macroblock. This is a typical example of the need to change the implementation method of ASIC, DSP, CPU, etc. depending on the usage situation.

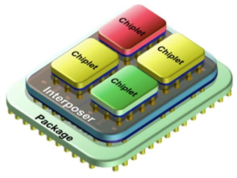

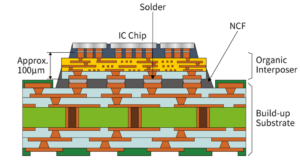

Chiplet IP Design

The semiconductor industry is experiencing a new wave of growth driven by the Internet of Things (IoT), big data, and artificial intelligence (AI). It features a heterogeneous computing environment, a distributed environment by chiplets and a scalable, reconfigurable and intelligent systems. In response to the need for such semiconductor innovation, it is expected that progress will be made by maintaining Moore's Law even below 2 nm through 3D miniaturization, such as "chiplet technology" in which multiple semiconductor chips are mounted on a single glass substrate using thin-film wiring. We provide system design by automatically generating integrated chiplet IP for large-scale systems such as processor IP, audio, image, 3D signal processing IP, communication IP, encryption IP, AI IP, and general-purpose IP. The introduction of chiplets can improve the rapid data control between on-chip buses and external memory controllers, which is a challenge in SoC designs.

It is possible to combine chiplets from different process nodes (generations of microfabrication technology) and different process technologies (logic, memory, analog ICs, RF circuits, power semiconductors, etc.) in a single package.

Chiplet

Structure

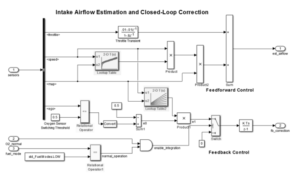

Model-based Design

Chiplet IP can also be used for model-based design using Matlab/Simulink and automatic design using Vivado of Xilinx. These design methods are effective in writing specifications for large-scale physical cyber systems such as autonomous vehicles, robots, and IoT by minimizing the need for actual machine manufacturing and by repeatedly performing simulations at the design stage. When implementing an H.264 video encoder, do you first write the entire system in C++ and then implement the MPEG processing part with MPU software, DSP firmware, or implement a dedicated MPEG processing circuit with HW? will be determined later during implementation. Since it is easy to reuse and brush up models and verification data, it not only improves efficiency during development, but also plays a role in passing on improvements to the next generation of development. This leads to reduced production costs and improved quality. We provide a system that can automatically generate IP modules that match usage conditions by inputting specifications. Set design parameters according to the usage environment, and generate an IP core from the parallelized standard algorithm using IP module generation software.

Simulink

Automatic Code Generation

Automatic code generation, which uses extensions of model-based development tools such as MATLAB/Simulink. Products include MATLAB Coder. Significantly improve current automatic code generation by automatically generating task graphs and performing optimal scheduling. Programs can be automatically generated without human intervention, but depending on the model description, unintended code may be generated, so we usually check the details while reviewing.

Task Scheduling